32ビット・スペシャル・マイコンから ビンテージICまで…わがままチップ作り放題!

# のMAX100ライタのDVD付き! FPGA電子工作 スーパーキット

圓山 宗智 著

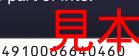

# 大容量ワンチップFPGA MAX10搭載基板

表面 10M08SAE144C8G(アルテラ) コンフィグレーション&ユーザ用FLASH内蔵

裏面

大規模アプリ製作に! SDRAM(別売)搭載可能

- - Quartus Prime Lite Edition/Qsys

- ModelSim Altera Starter Edition

- Nios II 32ビットCPUコア

- Nios II EDS (ソフトウェ<mark>ナ航に</mark>開発する。 • サンプル・ファデェクト - ド

## 第 1 部 MAX 10 デバイスと評価ボードのハードウェア

第 章 最新のFLASHメモリ内蔵型FPGAがあなたの手に

# CQ版MAX 10評価ボードの誕生

## ●はじめに

本書は、アルテラ社のFLASHメモリを内蔵した最新版FPGA(Field Programmable Gate Array) MAX 10 を搭載した基板およびその開発環境一式を収録した DVD-ROM を付属しています.

FPGA はその中に CPU(Central Processing Unit), メモリ, 通信機能, タイミング・シーケンサ, 演算アクセラレータ, 画像処理機能, 音声処理機能, ディジタル・フィルタなど自分の好きな論理機能を自由に組み上げることができます. 仕事でも趣味でも, 手軽に自己実現できるデバイスであり, 大いに楽しむことができるものです.

特に今回採用したアルテラ社のMAX 10 は、 FLASHメモリを内蔵するなど優れた特長を持つ FPGAであり、とても使いやすいものです。

しかし一般的に FPGA をコンフィグレーションする (論理機能を書き込む)ときには、JTAG (Joint Test Action Group)ケーブルという専用ツールが必要です。 CQ 出版社の過去のいくつかの雑誌付属 FPGA 基板では、ここがあまりよく練られておらず使い勝手がよくなかったように感じます。そこで今回の付属基板にはアルテラ社の USB Blaster と等価な機能を持つ USB-JTAG 変換基板もしっかり用意しました。これら付属基板と DVD-ROM だけで FPGA の開発全てを行うことができます。大いに遊んでいただきたいと思います。

## アルテラ MAX 10 FPGA とは

## MAX 10 は FLASH メモリ内蔵マイコンを自 作できる FPGA

アルテラ社の MAX 10 は、不揮発性 FLASH メモリ を 搭 載 し た TSMC(Taiwan Semiconductor Manufacturing Co., Ltd.)社の 55nm プロセスを使用した最新型の FPGA です。従来の MAX シリーズは CPLD(Complex Programmable Logic Device)でしたが、MAX 10 は本格的な FPGA デバイスであり、規

模が大きい論理回路を実装することができます.

MAX 10 は、デバイス本体にコンフィグレーション・データ格納用の FLASH メモリを内蔵しているので、外部に ROM を置く必要がありません.

1

さらに FLASH メモリの一部はユーザが使用でき、かつアルテラ社のソフト CPU コア Nios II も実装できます。12 ビット A-D 変換器も内蔵しており、3.3V 単一電源で動作するデバイスもラインアップされています。MAX 10 があれば、ユーザ独自の FLASH メモリ内蔵マイコンを自作することもできるのです。

## ●付属基板に搭載する MAX 10

MAX 10 は、ロジック・エレメント数として 2,000 個の最小規模品から 50,000 個の最大規模品まで 7 段階の製品がラインアップされています。今回の付属基

#### 表1 付属基板に搭載するMAX 10 FPGAの仕様

実際に基板に搭載されるデバイスはES (Engineering Sample)品である.

| 項目          | 内 容                                |  |

|-------------|------------------------------------|--|

| ベンダ         | アルテラ                               |  |

|             |                                    |  |

| 製品シリーズ      | MAX 10 FPGA                        |  |

| 製品型名        | 10M08SAE144C8G                     |  |

| プロセス        | TSMC 55nm Embedded FLASH           |  |

| 7 - 27      | プロセス技術                             |  |

| ロジック・エレメント  | 8K                                 |  |

| M9Kメモリ      | 378K ビット                           |  |

|             | 2496Kビット(コンフィグレーション                |  |

| FLASHメモリ    | 用+ユーザ用合計)                          |  |

|             | 1376Kビット(ユーザ用最大値)                  |  |

| 18×18乗算器    | 24 個                               |  |

| PLL         | 2個                                 |  |

| LVDS        | 専用Rx/Txチャネルまたはエミュレ                 |  |

| LVDS        | ーション出力チャネル×41ペア                    |  |

| コンフィグレーション数 | 最大2コンフィグレーション・イメー                  |  |

|             | ジを記憶可能                             |  |

| A Date HARD | 12ビット×1ユニット,変換レート                  |  |

| A-D変換器      | 1MSPS <sub>max</sub> , アナログ入力端子×9本 |  |

| カロッカ発転型     | リング・オシレータ内蔵                        |  |

| クロック発振器     | $(55M \sim 116MHz)$                |  |

| I/O本数       | 101本                               |  |

| 電源          | 3.3V 単一電源                          |  |

| 18 m 4 . 35 | EQFP-144(20mm×20mm,                |  |

| パッケージ       | ピン・ピッチ0.5mm)                       |  |

| L           |                                    |  |

見本

# 第 2 章 FLASH内蔵によるFPGAの新たなパラダイム

# MAX 10 FPGAデバイスの ハードウェア研究

## ●はじめに

本章では、最初に FPGA とはどういうデバイスなのか、またどういうことができるのかを簡単に解説します。 FPGA の可能性とその奥深さ、面白さを感じ取ってほしいと思います。 その次に、付属基板で採用したアルテラ社の MAX 10 についてそのデバイスの詳細を説明します。

FPGA というデバイスは、それ自体は大変複雑で高度な技術が使われています。ところが、ユーザはそのデバイスの中身を事細かに理解しきる必要は必ずしもありません。別章で解説する開発ツールが細かいことはほとんどサポートしてくれます。ユーザは自分が実現したい論理機能の設計に集中すればいいのです。本章で解説する MAX 10 デバイスの各機能の多くも、知識として知っておく程度で十分でしょう。

ただし、FPGAできちんと認識しておかないといけないことは、その制限事項です。FPGAはとても柔軟なデバイスですが、実現できる論理規模やメモリ容量などには上限があり、クロック配線、端子機能、特殊機能、コンフィグレーション機能などにどうしても注意事項や制限事項が存在します。それらのうち、特に重要と思われるものは本章や後続の章で説明を加えてありますので、よく理解しておいてください。

## FPGA とは何か

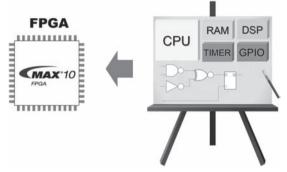

## ● FPGA は論理設計のための広大なキャンパス

データ処理やシーケンス処理など、ディジタル処理機能が必要なシステムの論理設計をする場合、ひと昔前までは、大量の TTL(Transistor Transistor Logic) IC や小規模 PLD(Programmable Logic Device)を組み合わせたプロトタイプ基板を作成するなど非常に手間がかかる思いをしましたが、ご存知の通り、今ではFPGA という強力な武器があります。

**図 1**に示すように、CPU(Central Processing Unit)、メモリ、周辺機能などの IP(Intellectual Property: 既存の設計資産やライブラリ)を自由に組み合わせ

図1 FPGAは論理設計のための広大なキャンパス

る、または独自の論理回路を自由奔放に設計するための広大なキャンパスが FPGA です。 論理機能は、Verilog HDLや VHDLというハードウェア記述言語 (HDL) で記述すれば、FPGA 用の開発ツールが FPGA デバイスの中のハードウェア・リソースに自動的にマッピングして、設計した通りの機能を実現してくれるのです。

## ●ディジタル・デバイスの主流組: SoC や MCU

ディジタル処理機能を持つ論理デバイスの代表格としては、スマートフォンやタブレット PC に入っている ARM Cortex-xx を内蔵したプロセッサなどの SoC (System on a Chip)や、多くの電子機器に組み込まれているマイコン (MCU: Micro Controller Unit)があります。 SoC や MCU は、図 2(a) に示すように、CPU や周辺機能などの論理機能や、A-D変換器などアナログ・モジュールなど、さまざまな機能モジュールが詰まっています(最近の SoC と MCU はその構造がほとんど同じであり、違うとすれば、MCU が SoC よりも若干論理規模が小さめで、かつ不揮発性のFLASH メモリを搭載している点くらいである)。

SoC や MCU は、性能、消費電力、コストを最適化することができる一方で、1枚のシリコンに固定化されているため一旦作ってしまうと機能変更できません。また SoC や MCU は、設計をスタートしてから実際のデバイスを手にするまでに何ヶ月もかかり、マス

\_

7

8

9

10

11

12

13

14

## 第 3 章 実験に、試作に、趣味に、 第 3 章 あれこれ手軽に使える小型FPGA基板

# MAX 10 FPGAを搭載した MAX 10-FB基板のハードウェア詳説

| 本書付属 DVD-ROM 収録関連データ                                    |                   |  |

|---------------------------------------------------------|-------------------|--|

| 格納フォルダ                                                  | 内 容               |  |

|                                                         | • MAX10-FB基板のガーバ・ |  |

| CQ-MAX10\text{\text{Board\text{\text{\text{MAX10-FB}}}} | データ               |  |

|                                                         | • 関連ドキュメント        |  |

## ●はじめに

本章では、MAX 10 FPGA を搭載した付属基板 MAX 10-FB 基板のハードウェアについて詳しく解説します.

## MAX10-FB 基板の概要

## ● MAX 10 FPGA を気軽に使うためのブレー クアウト基板

FLASHメモリを内蔵し単一電源で動作する FPGA デバイス MAX 10 を、ブレッド・ボードや自作のユニバーサル基板などの上で気軽に使うためのブレークアウト(脱獄)基板が MAX10-FB 基板です。その外観を写真1に、仕様を表1に、ブロック図を図1に示します。

## ● FPGA の I/O 電源はフレキシブルに設定可能

MAX 10 デバイスの外部 I/O 端子の各バンクの電源やアナログ・リファレンス電源は、それぞれ独立した電圧に設定できるので、全てを基板の外部コネクタに引き出してあります。それぞれ 3.3V で良い場合は、基板裏面のはんだジャンパで 3.3V 電源に接続できます。

#### ●基板上にクロック発振器を搭載

MAX 10 デバイスは、リング発振器を内蔵していますが、デバイス内蔵の PLL (Phase Locked Loop)に直接接続できませんので、PLL に接続できるグローバル・クロック端子に外部発振器 (48MHz) を接続してあります。内蔵 PLL によりさまざまな周波数のクロックを合成できます。

## ● SDRAM を搭載して大容量メモリ空間を自由 に使える

MAX10-FB 基板の裏面には、SDRAM を実装でき

#### 表1 MAX10-FB基板の仕様

| 項目                   | 内 容                                                                                                                                            |  |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 基板外形                 | 55.88mm × 35.56mm (22000mil × 14000mil)                                                                                                        |  |

| 層数/部品<br>実装面         | 2層基板/両面実装                                                                                                                                      |  |

| FPGA                 | アルテラ MAX 10「10M08SAE144C8G」                                                                                                                    |  |

| SDRAM                | 裏面未実装、パターンのみ、<br>搭載可能デバイス例は下記の通り<br>・512Mビット:AS4C32M16SA-6TCN/7TCN<br>(Alliance Memory)<br>・256Mビット:AS4C16M16SA-6TCN/7TCN<br>(Alliance Memory) |  |

| 電源                   | 外部3.3V 供給<br>(各 V <sub>CCIO</sub> , V <sub>CCA</sub> , ADC_V <sub>REF</sub> , REG_GND は個別に<br>コネクタに引き出してあり, はんだジャンパで共<br>通の3.3V と GND に接続可能)   |  |

| ユーザ用                 | 48MHz 発振器搭載可能(未実装)                                                                                                                             |  |

| クロック                 | SG8002DC-PCB-48MHz(エプソントヨコム)                                                                                                                   |  |

| ユーザ用<br>LED          | 3色 RGB フル・カラー LED×1 個                                                                                                                          |  |

| ユーザ用<br>スイッチ         | プッシュ・スイッチ×1個                                                                                                                                   |  |

| コンフィグ<br>レーション<br>回路 | nCONFIG用プッシュ・スイッチ×1個<br>CONFIG_SEL用ジャンパ×1個                                                                                                     |  |

| FPGA信号               | ブレッド・ボード用の上下1列コネクタに38本                                                                                                                         |  |

| 引き出し                 | 引き出し(2.54mmピッチのコネクタに合計49本引                                                                                                                     |  |

| 端子                   | き出し)                                                                                                                                           |  |

| FPGA                 | 付属基板「MAX10-JB」を重ねて、電源供給+コン                                                                                                                     |  |

| コンフィグ                | フィグレーション可能                                                                                                                                     |  |

| レーション                | (アルテラ社または3rd Party製のUSB Blasterでも                                                                                                              |  |

| 方法                   | コンフィグレーション可能)                                                                                                                                  |  |

るパターンがあります. 54 ピン TSOP II パッケージ に封入された SDR (Single Data Rate)型の SDRAM (Synchronous DRAM)を実装できます. 動作を確認 済みの推奨品は、256M ビットまたは 512M ビットの 16 ビット幅の SDRAM です. アルテラ社が提供する SDRAM コントローラで簡単にアクセスできます. 大量のデータを扱うときに便利です.

## ●動作確認用のフル・カラー LED とプッシュ・ スイッチ

MAX10-FB 基板にはユーザ動作確認用のフル・カラー LED とプッシュ・スイッチを搭載してあります. この基板単体でも簡単な論理設計の実験を\_Nios ↓

4

5

7

8

10

11

12

13

14

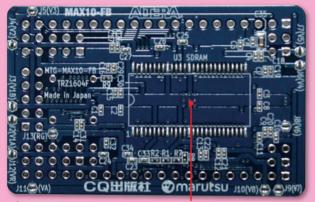

## 第 4 章 Quartus Primeから直接操作! コンフィグレーションにもデバッグにも使える!

# コンフィグレーション&デバッグ用 MAX10-JB基板のハードウェア詳説

| 本書付属 DVD-ROM 収録関連データ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                            |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--|

| 格納フォルダ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 内 容                                                        |  |

| CQ-MAX10\text{\text{\$\text{\$Y}}}Board\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\text{\$\ext{\$\ext{\$\text{\$\text{\$\exit{\$\ext{\$\ext{\$\exit{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\exit{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\exit{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\exit{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\ext{\$\exit{\$\ext{\$\exit{\$\exit{\$\exit{\$\exit{\$\exit{\$\exit{\$\exit{\$\exit{\$\exit{\$\exit{\$\exit{\$\exit{\$\exit{\$\exit{\$\exit{\$\exit{\$\exit{\$\exit{\$\exit{\$\exit{\$\exit{\$\exit{\$\exit{\$\exitit{\$\exit{\$\exit{\$\exit{\$\exit{\$\exit{\$\exit{\$\exit{\$\exit{\$\exit{\$\exit{\$ | <ul><li>MAX10-JB基板の<br/>ガーバ・データ</li><li>関連ドキュメント</li></ul> |  |

## ●はじめに

本章では、MAX 10 FPGA のコンフィグレーションおよびデバッグ用付属基板 MAX10-JB 基板のハードウェアについて詳しく解説します.

## MAX10-JB 基板の概要

## ● FPGA にはコンフィグレーションが必要

FPGA を動かすためには、実現しようとする論理機能に対応する情報を FPGA に送り込む、すなわち FPGA をコンフィグレーション(略してコンフィグともいう)する必要があります。 MAX 10 の場合は、下

## 表1 MAX10-JB基板の仕様

| Z                   |                                                                                                                           |  |  |

|---------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|

| 項目                  | 内 容                                                                                                                       |  |  |

| 基板外形                | 55.88mm × 35.56mm (22000mil × 14000mil)                                                                                   |  |  |

| 層数/部品<br>実装面        | 2層基板/片面実装                                                                                                                 |  |  |

| 実装部品                | 搭載部品はユーザ手配、ユーザ実装                                                                                                          |  |  |

| 機能                  | アルテラ USB-Blaster 等価機能                                                                                                     |  |  |

| 使用マイコン              | PIC18F14K50-I/P<br>(マイクロチップ・テクノロジー)<br>(3.3V ネイティブ動作)                                                                     |  |  |

| USBコネクタ             | USB mini B                                                                                                                |  |  |

| 電源供給                | USBバス・パワー MAX10-FB 側に電源供給可能                                                                                               |  |  |

| 電源電流<br>(3.3V)      | LT1963A-3.3使用:合計1.5A<br>(電源ICは面実装型で、SSOP-8またはSOT-<br>223いずれも実装可能)                                                         |  |  |

| PIC18マイコン<br>のプログラム | ・USB - Blaster 等価機能(JTAG 機能のみ)<br>・コンパイラ:XC8<br>・USB ライブラリ:最新 Microchip Libraries<br>for Applications 使用<br>・プログラムのソースは公開 |  |  |

| のFLASHメモ            | PIC18マイコンのFLASHメモリは、初期状態の「MAX10-FB」側から書き込み(PICマイコン用フラッシュ書き込み器「PICkit3」などは不要)                                              |  |  |

記の2種類のコンフィグレーション方法があります.

- (1) JTAG コンフィグレーション: JTAG ポートから 直接 FPGA 内の論理構造をコンフィグレーションする. 電源投入のたびに必要. 電源が落ちるとコンフィグレーション情報も消える.

- (2) 内部コンフィグレーション: あらかじめ JTAG ポート経由で内蔵 FLASH メモリにコンフィグレーション・データを書き込んでおく. 電源投入のたびに、その内蔵 FLASH メモリから FPGA 内の論理構造をコンフィグレーションする.

このいずれに関しても、一般的には USB Blaster と呼ばれるアルテラ社純正の USB-JTAG 変換ケーブル、またはその相当品を使って、開発ツール Quartus Prime が生成したコンフィグレーション・データをFPGA に送り込む必要があります.

## ● FPGA にはデバッグ環境の提供も必要

MAX 10 FPGA には、Nios II (Gen2)という 32 ビットの組み込み向け CPU コアを搭載できます。RTL で提供されているソフト IP です。CPU を内蔵できるので、そのソフトウェア開発時にはデバッグが欠かせませんが、FPGA デバイスの JTAG ポート経由で簡単にソース・レベル・デバッグできる機能がサポートされています。

このデバッグ操作にも、USB Blaster を使います.

## ■ MAX 10 FPGA のコンフィグレーション& デバッグ用基板

今回の MAX10-FB 基板上の FPGA のコンフィグレーションとデバッグ用に、USB Blaster 相当の機能を提供するのがもう 1 枚の付属基板である MAX10-JB基板なのです。その外観を写真1に、仕様を表1に、ブロック図を図1に示します。

MAX10-JB 基板は、USB Blaster の JTAG インターフェース機能のみをサポートします。AS(Active Serial) インターフェースや PS(Passive Serial) インターフェースはサポートしません。

MAX10-JB 基板は、部品を実装していない生基板

見本

15

MAX10-JB 基板の概要

## 第 5 章 MAX 10によるPICマイコンFLASH書き込み器の構造と, PICマイコンによるUSB Blaster等価機能の実現

# MAX10-FB基板と MAX10-JB基板の協調動作の仕組み

| 本書付属 DVD-ROM 収録関連データ                   |                                          |       |  |

|----------------------------------------|------------------------------------------|-------|--|

| 格納フォルダ                                 | 内 容                                      | 備考    |  |

| CO-MAX10¥PIC¥USB JTAG¥firmware         | USB Blaster 等価機能用PICマイコン・プログラムのプロジェクト一式  |       |  |

| _                                      |                                          | いずれも参 |  |

|                                        | PICマイコンのバイナリ・ファイル(hex)をNios IIプログラムにインク  | 考用であり |  |

| CQ-MAX10\PIC\hex2c                     | ルードするためにCソース・コードに変換するユーティリティ(ANSI C      | 読者が使用 |  |

|                                        | でコンパイルして使用)                              | する必要は |  |

| CQ-MAX10\Projects\PROJ_PIC_Programmer  | PICマイコンのFLASH書き込み器としてのMAX 10 FPGA プロジェクト | ない    |  |

| CQ-MAXIV#PIOJECUS#PROD_PIC_PIOGIANUNEI | (Quartus Prime, Nios II Eclipse用)        |       |  |

## ●はじめに

本章の前半では、MAX10-JB 基板上の PIC マイコンの FLASH メモリにプログラムを書き込むために MAX10-FB 基板(出荷時点)の FPGA に仕込んだシステムについて解説します。その実現のために FPGA

#### 表1 PIC18F14K50-I/Pの仕様概要

| 表 1 PIC18F14K50-I/Pの仕様似要                               |                                                                                                                                 |  |  |

|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--|--|

| 項目                                                     | 内 容                                                                                                                             |  |  |

| 型名                                                     | PIC18F14K50-I/P                                                                                                                 |  |  |

| パッケージ                                                  | DIP-20 ピン                                                                                                                       |  |  |

| FLASHメモリ                                               | 16Kバイト                                                                                                                          |  |  |

| EEPROM                                                 | 256バイト                                                                                                                          |  |  |

| RAM                                                    | 768バイト                                                                                                                          |  |  |

| CPU                                                    | <ul><li>・8ビット高性能RISC</li><li>・16ビット固定長命令</li></ul>                                                                              |  |  |

| 動作条件                                                   | ・電源電圧: 2.7V ~ 5.5V<br>・最大動作周波数: 48MHz                                                                                           |  |  |

| USB デバイス<br>機能                                         | ・USB 2.0 準拠 ・フル・スピード(12Mbps) またはロウ・スピード(1.5Mbps) ・コントロール転送、インタラプト転送、アイソクロナス転送、バルク転送 ・16エンドポイントまでサポート(双方向8組) ・256バイト・デュアル・ポートRAM |  |  |

| A-D変換器                                                 | ・10ビット分解能                                                                                                                       |  |  |

| アナログ・<br>コンパレータ                                        | ・2ユニット,Rail-to-Rail 入力                                                                                                          |  |  |

| タイマ       ・拡張型コンペア/キャプチャ/PWM(E0)         ・PWM出力本数:1~4本 |                                                                                                                                 |  |  |

| 同期シリアル                                                 | 3ワイヤSPIマスタまたはI <sup>2</sup> Cマスタ/スレーブ                                                                                           |  |  |

| 非同期シリアル                                                | UART                                                                                                                            |  |  |

内に特殊な SPI モジュールを組み込んでありますが、 このモジュールについては、別冊の「実践編」の中で論 理設計と論理検証の例題として詳しく解説します.

また後半では、PIC マイコンにプログラムを書き込んだ以降、MAX10-JB 基板は USB Blaster 等価機能を持ちますが、その仕組みと PIC マイコンのプログラム内容について解説します注。

## PIC マイコン書き込み器としての MAX10-FB 基板

# ● MAX10-JB 基板に搭載した PIC18F14K50-I/P の概要

MAX10-JB 基板に搭載した PIC マイコンの仕様概要を表1に、ピン配置図を図1に示します。この PIC マイコンは USB 2.0 のデバイス側の機能を持っており、ローコストな USB 機器を自作するのに適しています。この PIC マイコンの FLASH メモリにプログラムを書き込む必要があります。

## ●初期出荷状態の MAX10-FB 基板は PIC 書き 込み器になっている

初期出荷状態の MAX10-FB 基板はその出荷検査も 兼ねて、搭載する MAX 10 デバイスの FLASH メモ リにコンフィグレーション・データが書き込まれてい ます。

また、本章で説明するFLASHメモリ書き込み方式は、PICマイコンのFLASHメモリに関するものである。MAX 10内のFLASHメモリに関するものではないので混同しないようにすること。

注)本章の内容は、MAX10-FB基板とMAX10-JB基板の協調動作の仕組みに関する技術情報を提供するものであり、付録のMAX10-FB 基板とMAX10-JB基板を使うだけであれば必ずしも理解する必要はない.

## 第 2 部 MAX 10 FPGA 開発入門

## 第 6 章 Quartus Prime Lite Editionと関連ツールを インストールして,基板とPC間の接続確認を行う

# MAX 10用開発環境のインストール

| 本書付属 DVD-ROM 収録関連データ                                                |                                 |  |

|---------------------------------------------------------------------|---------------------------------|--|

| 格納フォルダ                                                              | 内 容                             |  |

|                                                                     | Quartus Prime Lite Edition      |  |

| CQ-MAX10\text{YQuartus_Prime\text{YQuartus-lite-15.1.1.189-windows} | • Nios II EDS                   |  |

|                                                                     | ModelSim-Altera Starter Edition |  |

## ●はじめに

本章では、MAX 10 FPGA デバイスの開発に必要なツール一式をインストールします。実際の各ツールの使用方法は後続の章で説明します。

また、前の章までに作成した、MAX10-FB 基板と MAX10-JB 基板を USB ケーブルで PC に接続して、正常に認識されるかどうかの確認を行います.

## MAX 10 FPGA 用開発ツール

## ●インストールするツールの種類

今回、MAX 10 FPGA の開発をするためにインストールするツールのうち主なものを**表 1** に示します. FPGA の統合化開発環境 Quartus Prime. 論理シミュ

#### 表1 インストールする主なツール

| アイコン | ツール名                                   | 説 明                                                                                                          |  |

|------|----------------------------------------|--------------------------------------------------------------------------------------------------------------|--|

| 0    | Quartus Prime<br>Lite Edition          | FPGAの統合化開発環境. ファイル編集, 論理合成, 配置配線, タイミング検証, コンフィグレーション用ファイル生成などを行う.<br>Qsysを起動して, Nios IIコアなど各種IPを含むシステム設計が可能 |  |

|      | Quartus Prime<br>Programmer            | コンフィグレーション用ファイルのFPGAへの書き込みツール.<br>MAX10-JB基板のUSB Blaster等価機能を介して、MAX10-FB基板上のMAX 10への書き込みか可能                 |  |

| M    | ModelSim-Altera<br>Starter Edition     | 論理シミュレーション用ツール.<br>FPGAの固有IPのモデルも搭載しており、FPGA全体をシミュレーションできる                                                   |  |

| (2)  | Nios II EDS<br>(Embedded Design Suite) | Nios IIのCプログラム統合化開発環境.<br>MAX10-JB基板のUSB Blaster 等価機能を介して,MAX 10内に構築したNios II コアのソース・<br>レベル・デバッグが可能         |  |

| 名前                                      | 更新日時             | 種類                     | サイズ          |

|-----------------------------------------|------------------|------------------------|--------------|

| arria_lite-15.1.0.185.qdz               | 2015/10/23 9:43  | QDZ ファイル               | 509,630 KB   |

| cyclone-15.1.0.185.qdz                  | 2015/10/23 9:42  | QDZ ファイル               | 475,035 KB   |

| cyclonev-15.1.0.185.qdz                 | 2015/10/23 9:31  | QDZ ファイル               | 1,178,911 KB |

| max10-15.1.0.185.qdz                    | 2015/10/23 9:30  | QDZ ファイル               | 347,029 KB   |

| max-15.1.0.185.qdz                      | 2015/10/23 9:31  | QDZ ファイル               | 11,536 KB    |

| NodelSimSetup-15.1.0.185-windows.exe    | 2015/10/23       | ックリック ) 37             | 1,157,309 KB |

| QuartusHelpSetup-15.1.0.185-windows.exe | 2015//0/23 12:31 | アフワーション<br>ソミジーファフーション | 299,035 KB   |

| QuartusLiteSetup-15.1.0.185-windows.exe | 2015/10/30 5:23  | アプリケーション               | 1,479,208 KB |

| QuartusSetup-15.1.1.189-windows.exe     | 2015/12/05 4:33  | アプリケーション               | 1,665,040 KB |

| update info.txt                         | 2015/12/05 4:34  | テキストドキュメント             | 1 KB         |

図1 必要なインストール用ファイルを同一階層に置く

見本

3

4

5

6

7

8

9

10

11

19

19

14

**1**5

## 第 **了** 章 LEDチカチカをネタにして, 第 **了** 章 Quartus Primeの一通りの使い方をマスタしよう

# FPGA開発ツール Quartus Prime入門

| 本書付属 DVD-ROM 収録関連データ            |                          |                          |  |

|---------------------------------|--------------------------|--------------------------|--|

| 格納フォルダ 内容                       |                          | 備考                       |  |

| CO MAY10YDrojostsYDDOI COLODIED | フル・カラー LEDチカチカ回路の        | 本章では、このプロジェクトを読者がゼロから作成す |  |

| CQ-MAXIU#PIOJECUS#PROJ_COLORLED | プロジェクト一式(Quartus Prime用) | る方法を説明する。参考用として提供する。     |  |

## ●はじめに

本章では、フル・カラー LED のチカチカ点滅回路 を題材にして、Quartus Prime による基本的な開発の 流れを一通りマスタしましょう。

新規プロジェクトの作成、Verilog HDL 記述の編集、解析、合成、外部端子への信号アサイン、配置・配線を含めた FPGA のコンパイル、FPGA のコンフィグレーションまでの基本的な流れを説明します。

また、FPGA の内部信号をロジック・アナライザ(ロジアナ)のように観測できる SignalTap II という機能を Quartus Prime が持っており、その使い方も説明します.

最後に、タイミング解析の例として、設計した論理 回路の最高動作周波数を確認してみます.

# Quartus Prime による FPGA の開発フロー

まず、Quartus Prime による FPGA の開発フロー について説明します。 図1 にその全体フローを示します.

## ●新規プロジェクトの作成

Quartus Prime では、FPGA 内に構築する設計対象をプロジェクトとして管理します.一番最初にプロジェクト・ファイル(xxx.qpf)を作成します.

Quartus Prime には新規プロジェクトを作成するための支援機能(ウィザード)があり、プロジェクト名とプロジェクト格納場所の指定、対象 FPGA デバイスの指定、使用する HDL 言語(Verilog HDL、System Verilog、VHDL)の選択などを、ウィザードの指示に従って行うことで新規プロジェクトを生成できます。

なお、本書では HDL 言語として、Verilog HDL を使用することを基本前提とします.一部、C 言語混在

シミュレーションについて説明するときに System Verilog を使用します.

既存のプロジェクトをベースにした別の設計を行う場合は、プロジェクト・フォルダをそのままコピーしてフォルダ名を変更して、プロジェクト内の設計内容を変更することで対応できます。または、新規プロジェクト作成用ウィザード内でも既存プロジェクトの設定内容を引き継ぐこともできます。

## ●論理記述(Verilog HDL)の作成

FPGAの最上位(トップ)階層から、下位の個々のモジュールまで、一連の論理記述(Verilog HDL)を作成します、論理設計の基礎や、Verilog HDLの書き方や文法については、姉妹書の実践編の中で詳細に説明しますので、わからなくてもとりあえずこのまま入力しておいてください。

Quartus Prime テキスト・ファイルの編集機能を使って論理記述を作成し、プロジェクトに登録していきます。 論理記述ファイルを Quartus Prime 上で新規作成すれば自動的にプロジェクトへ登録されますが、既存の論理記述を流用する場合は、マニュアルで追加します。

Nios II CPU コアなどの各種 IP を含むシステムは Qsys を使って設計できます. そのシステムを FPGA に組み込む場合は,対応するインスタンス化記述を論 理記述へ追加します.

必要に応じて、FPGA の固有機能(ロジアナ機能の Signal Tap II や、デュアル・コンフィグレーション機能など)も論理記述へ追加します.

## ●論理シミュレーション

作成した論理記述が簡単なものであれば、いきなり FPGA に実装して動作確認する場合もありますが、一般的には論理シミュレーションでその機能動作を検証

見本

## 第 章 PLLの使い方とパワーONリセット回路の 作り方をマスタしよう

# 論理回路の土台! MAX 10のクロックとリセットの基礎

| 本書付属 DVD-ROM 収録関連データ             |                         |                         |  |  |

|----------------------------------|-------------------------|-------------------------|--|--|

| 格納フォルダ 内容                        |                         | 備考                      |  |  |

| CQ-MAX10\Projects\PROJ_COLORLED2 | フル・カラー LED 階調明滅回路のプ     | 本章では、このプロジェクトを読者がゼロから作成 |  |  |

| CQ-MAXIU#FIOJECUS#PROJ_COLORLEDZ | ロジェクト一式(Quartus Prime用) | する方法を説明する.参考用として提供する.   |  |  |

## ●はじめに

本章では、論理回路の土台になるクロックとリセットについて、特に FPGA 設計で必要になる知識をマスタします.

ここでは、さまざまな周波数のクロックを合成できる PLL(Phase Locked Loop)の使い方と、外部リセット信号を省略するためのパワー ON リセット回路の作り方について説明します。フル・カラー LED の階調明滅回路を題材にします。

## PLL とパワー ON リセット回路

### ● PLL とは

FPGA も必ずといっていいほど PLL (Phase Locked Loop) を搭載しています. PLL は入力クロックに対して逓倍と分周を施すことで、さまざまな周波数のクロックを合成できます.

MAX 10 が持つ PLLでは、周波数だけでなく、位相やデューティ比の設定もできます。図1に示すALTPLLという IP の場合、1本の入力クロックから最大5種類のクロックを生成できます。これ以外にも輻射ノイズの計測値を低減させるための周波数拡散機能や、動作中に動的に再設定できる機能などもあり、

| 入力                         | ALTPLL | -  |                                                                                             |

|----------------------------|--------|----|---------------------------------------------------------------------------------------------|

| f <sub>in0</sub> クロック      | inclk0 | с0 | 出力クロック0<br>$+ f_{c0} = f_{in0} \times M_0/D_0$<br>出力クロック1                                   |

|                            |        | с1 | 出力クロック1<br>$f_{c1}=f_{in0}\times M_1/D_1$                                                   |

|                            |        | c2 | 出力クロック? $f_{c1} = f_{in0} \times M_1/D_1$ 出力クロック2 $f_{c2} = f_{in0} \times M_2/D_2$ 出力クロック3 |

| M。: 逓倍率                    |        | сЗ | $f_{c3} = f_{in0} \times M_3/D_3$                                                           |

| <i>D</i> <sub>n</sub> :分周率 |        | с4 | $f_{c4} = f_{in0} \times M_4/D_4$                                                           |

#### 図1 PLLの概要

ALTPLLというIPの基本機能を示す.

非常に多機能です.

## ●本書での PLL 設定の基本

本書では原則として、PLLへの入力クロックの周波数は MAX10-FB 基板上の発振器から供給される 48MHz とし、PLL からユーザ論理に供給するクロックの周波数は 50MHz とします.

プロジェクトによっては、FPGA内で使用するIPの仕様に依存して、位相や周波数を変えたクロックもPLLで生成することがあるので、その都度説明します.

## ●パワー ON リセット回路とは

論理回路内のフリップフロップ(順序回路)は、放っておくと初期状態が不定なので、通常はリセットが必要です。前章のPROJ\_COLORLEDの事例では、リセット信号はMAX10-FB基板上のタクト・スイッチで入力しました。この基板上でユーザが使えるスイッチは一つだけなのでリセット用に使うと他には使えなくなります。

このような場合、パワー ON 時に電源電圧の立ち上がりを検出したら自動的にデバイス内にリセット信号を一定期間だけ送るパワー ON リセット回路があると便利です。マイコン(MCU: Micro Controller Unit)などでは一般的に内蔵している機能です。

# ● MAX 10 自体はパワー ON リセット回路を内蔵している

MAX 10 デバイスそのものには、実はパワー ON リセット回路が内蔵されています。これは電源立ち上がりを検出したら、内蔵 FLASH メモリのコンフィグレーション・データを使って自動的に FPGA をコンフィグレーションするために用意されています。

見本

15

## 第 9 章 MAX 10のFPGAには2種類の コンフィグレーション・データを格納できる

# MAX 10のデュアル・ コンフィグレーション機能を活用

| 本書付属 DVD-ROM 収録関連データ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                          |                                              |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------------------------------------|--|

| 格納フォルダ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 内 容                                                      | 備考                                           |  |

| CQ-MAX10\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foots\foo | デュアル・コンフィグレーション用のプロジェクト×2種類:FPGA1とFPGA2 (Quartus Prime用) | 本章では、このプロジェクトを読者がゼロから作成する方法を説明する、参考用として提供する. |  |

## ●はじめに

本章では、MAX 10 FPGA の大きな特徴であるデュアル・コンフィグレーション機能の活用方法をマスタしましょう。デュアル・コンフィグレーション機能を使うと、2種類のコンフィグレーション情報を MAX 10 の FLASH メモリに記憶させることができ、例えば、FPGA の起動時にユーザがどちらを使うかを自由に選択できるようになります。

ここでは前章までに作成したフル・カラー LED の 色変化点滅回路と階調明滅回路の 2 種類のコンフィグ レーション・データを FLASH メモリに書き込んで、 それぞれを FPGA の起動時に選択して動作させてみ ます.

## デュアル・コンフィグレーション機能 とは

### ●デュアル・コンフィグレーションの基本機能

デュアル・コンフィグレーションの流れの一例を**図** 1 に示します.

まず、2種類のプロジェクトから生成したコンフィグレーション・ファイルxxx.sofをそれぞれ合体して $output_file.pof$ というファイルを作成し、MAX~10のコンフィグレーション用FLASHメモリ(CFM0 およびCFM1/CFM2)に書き込んでおきます。

MAX 10 FPGA に 電 源 印 加 す る か, ま た は nCONFIG 信号に"L" レベルのパルスを与えると (MAX10-FB 基板の SW2 を押すと), FLASH メモリ 内のコンフィグレーション・データがデュアル仕様ならば, CONFIG\_SEL 端子のレベルをチェックし, "L" レベルなら CFM0 に書き込んだデータで FPGA をコンフィグレーションし、"H"レベルなら CFM1/CFM2 に書き込んだデータでコンフィグレーションします.

## ●デュアル・コンフィグレーションの高度な機能

デュアル・コンフィグレーション機能は、単に2種類のコンフィグレーション・データを選択するだけではありません.

2種類のコンフィグレーション・イメージを動作中でもダイナミックに切り替えることができますし、システムに組み込まれた状態で、リモート・システム・アップグレードをすることができます。

また、出荷時のコンフィグレーション・イメージを 片方の領域に入れて、システム・アップグレード時の 新しいイメージはもう一方の領域に入れるようにする と、もし、アップグレード後に問題が起こった際も出 荷状態に切り替えることができます(フェイルセーフ・アップグレード機能).

## ●デュアル・コンフィグレーション使用時の注意

デュアル・コンフィグレーション機能を使う場合 は、下記の点を考慮してください.

- Quartus Prime の個々のプロジェクトから生成する コンフィグレーション・ファイルは、デュアル・コ ンフィグレーション用の圧縮ファイル形式にするこ

- ●2種類のコンフィグレーション・ファイルは, Quartus Prime内のConvert Programming Files というツールで合体する.

- デュアル・コンフィグレーション機能を使う場合は、アルテラ社から提供される専用デュアル・コンフィグレーション用 IP をユーザ論理内に組み込むこと. この IP は、リモート・システム・アップグレード機能なども含むが、単に FPGA の立ち上げ時に 2 種類のコンフィグレーション・データを選択するだけのケースでも組み込む必要がある.

- FPGA 内のメモリ・ブロック (M9K RAM) に初期値

PAMIL NIIII THE PART OF THE P

# 第 **10** 章 無償の論理シミュレータで FPGAをホイホイ論理検証する手順をマスタしよう

# ModelSim Altera Starter Edition による論理シミュレーション入門

| 本書付属 DVD-ROM 収録関連データ              |                        |                        |  |

|-----------------------------------|------------------------|------------------------|--|

| 格納フォルダ                            | 内 容                    | 備考                     |  |

| CQ-MAX10\perojects\peroj_COLORLED | フル・カラー LEDチカチカ回路のプロ    |                        |  |

|                                   | ジェクト一式(Quartus Prime用) | 前章までに作成したプロジェクトを使って論理シ |  |

| CQ-MAX10\projects\proj_COLORLED2  | フル・カラー LED 階調明滅回路のプロ   | ミュレーションを実行する           |  |

|                                   | ジェクト一式(Quartus Prime用) |                        |  |

## ●はじめに

本章では、アルテラ社から無償で提供されている論理シミュレーション用ツール ModelSim Altera Starter Edition(以下、ModelSim と記述)の使い方について解説します。

題材としては、これまでの章で解説した、フル・カラー LED チカチカ回路 PROJ\_COLORLED と、階調明滅回路 PROJ\_COLORLED2 をそれぞれ使って、MAX 10 FPGA 全体を論理シミューションしてみます。

## 論理シミュレーションの 基本的な考え方

## ●本書では RTL 設計をベースとする

FPGAの論理設計を行う場合、最も抽象度が低い レベルは、回路図上で論理ゲートを直接組み上げてい く設計です。しかし、この設計エントリ方法は論理合 成ツールの性能が向上した今ではほとんど使わないで しょう。

論理ゲートから1段階高い抽象レベルはRTL (Register Transfer Level)です。Verilog HDLやVHDLといったハードウェア記述言語で表現できるもので、基本的には内部回路のレジスタ(フリップフロップ)だけは明確に定義して、そのレジスタ間の論理をブール式や条件式などで抽象化する記述方法です。

論理合成ツールを使えばRTLから論理ゲートへ自動変換でき、現在では非常に効率の良い合成結果が得られるようになっています。RTL記述は抽象度が高いといっても、そこから論理ゲートで構成される回路をほぼ類推できるので、テキスト・エディタで記述で

きる便利な回路図のような感じです。本書での論理設計はこの RTL レベルで行います。

## ●論理シミュレーションとは

LED をチカチカする程度の簡単な論理回路の場合、いきなりハードウェア記述言語 Verilog HDL で回路を記述して FPGA をコンフィグレーションし、動作確認しながら仕上げることもできるでしょう。実際、ここまでに取り上げた LED 点滅回路は、筆者もそうやって作成しました。

しかし、もっと複雑な論理回路を設計する場合、FPGAによる実機動作確認だけではデバッグしきれません。Quartus Prime がサポートするロジアナ機能Signal Tap II を使う手もありますが、FPGAのリソースを消費するし、見たい信号やトリガ条件を変更するだけでも、毎回 FPGA 全体をコンフィグレーションし直す必要があり、デバッグ効率は良くありません。

よって、論理設計においては、設計した論理回路の動作を PC 上でシミュレーションして、その内部信号やシステム動作が所望の通りかどうかを確認する作業が欠かせません。

# ●ハードウェア記述言語はシミュレーションのための言語

余談ですが、そもそも Verilog HDL というハードウェア記述言語は、論理シミュレータを作る側の人にとって都合の良い言語なのです。言語バージョンが上がるたびに改善されてきましたが、設計者のための言語というよりは、EDA(Electronic Design Automation)ツール開発者のための言語のようでした。

このあたりの楽しい(?)不平不満については、姉妹書の実践編の中で語ってみたいと思います

2

5

10

11

12

13

14

#### Nios II システム開発入門 第3部

# Nios IIコアの概要とその開発フローをマスタしよう

# Nios IIシステムの概要

## ●はじめに

本章では、Altera 社から提供されている RTL ベー スのソフト CPU コア Nios II の概要とその開発フロー について説明します. 具体的な設計事例は次章以降で 説明します.

## Nios II コアとそのシステム

## ● MAX 10 で使えるコアは Nios II Gen 2

Nios II コアには、Classic と Gen 2の2種類があり ます. 基本的に命令コードはバイナリ・コンパチブル ですが、キャッシュ関係の仕様(キャッシュ・バイパ ス関係)が異なっています.

開発環境 Quartus II Ver14.1 以降から Gen 2 だけ がサポートされており、MAX 10で使えるコアも Gen 2のみです. 以下の説明で Nios II と表記したも のは全て Gen 2 コアを指します.

#### ●本書では Nios II/e コアを使う

Nios II コアには2種類あります.表1にその機能 比較を示します. Nios II/e(Economy コア)は無償で すが、機能は限定されており、クロック当たりの性能 は低いです. Nios II/f(Fast コア)は有償ですが、高 機能でクロック当たりの性能も高いです.

本書では、無償の Nios II/e コアを使ったシステム 設計事例を説明します. Nios II/e はキャッシュやメ モリ管理ユニット(MMU)などのサポートがなく、か つ命令性能も低いですが、組み込み用のシンプルなシ ステム・コントローラとしては十分な機能があり、論 理規模も小さく、FPGAのLE(Logic Element)をあ まり消費しないという特長があります.

#### ● Nios II コアのブロック図

Nios II コアのブロック図を図1に示します. Nios Ⅱコアは機能仕様をユーザがコンフィグレーションで きるようになっており、必要な機能だけを選択できま す. カスタム命令の追加も可能であり、クリティカル な処理をハードウェア化した命令を追加することで, システム性能を向上させることができます.

本書の設計事例に組み込む Nios II/e コアには、図 1内で(\*)を付した JTAG デバッグ・モジュールと内 部割り込みコントローラをオプション追加して使いま す.

## ● Nios II コアの詳細仕様を理解せずとも開発で きる

Nios II コアの論理を FPGA に組み込む作業は設計 ツールにより自動化されています. ソフトウェア開発 はC言語ベースでありデバイス・ドライバも自動生 成されます. これらのサポートによって、Nios IIコ アの低レベルな階層の詳細仕様を理解することなく開 発を進められるようになっています.

Nios II コアの詳細アーキテクチャや命令仕様につ いて詳しく知りたいときは、参考文献(1)を参照して ください.

## ● Nios II のシステム構成と Avalon インター フェース

Nios II コアにより構成するシステム例を図2に示 します.

図2の一番上にバス・マスタになる Nios II コアと DMAC(Direct Memory Access Controller)がありま す. Nios II コアは、命令を取り込む命令バスとデー タのリード/ライトを行うデータ・バスが分離した ハーバード・アーキテクチャを採用しています.

図2の一番下には、バス・マスタからのアクセス を受けるスレーブ・モジュール(メモリや周辺機能)が あります.

## ●基本的なバス規格は Avalon-MM インター フェース

Nios II システムにおけるバス・マスタとスレーブ・ モジュールの間のバス・インターフェース規格として は、Avalon-MM インターフェースが採用されていま す. MMとは Memory Mapped の略であり、アドレ

## 第 12章 Nios IIシステムのハードウェア設計、ソフトウェア設計、 第 12章 論理シミュレーションまで全部通しでやってみよう

# Nios IIシステムでLチカ

| 本書付属 DVD-ROM 収録関連データ |                                                                                      |                                                                                             |  |

|----------------------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--|

| 格納フォルダ               | 内 容                                                                                  | 備考                                                                                          |  |

|                      | Nios II によるフル・カラー LED 点滅動作のプロジェクトー式 (Quartus Prime用, Nios II EDS用, ModelSim Altera用) | 本章では、このプロジェクトを読者がゼロから<br>作成する方法を説明する(参考用として提供す<br>る). 本章で説明する手順が全て終わった状態の<br>プロジェクトを格納してある. |  |

## ●はじめに

本章では、前章で説明した Nios II システム開発の一連の手順を具体的に説明します。 Nios II システムを設計ツール Qsys を使って設計して、C言語により LED のチカチカ動作をさせてみます。 さらにハードウェアとソフトウェアを含めた論理シミュレーションの手法についても説明します。

最終的に FPGA のコンフィグレーション・データと Nios II のソフトウェアを MAX 10 の FLASH メモリに格納するので、本章で説明する手法をマスタすれば、オリジナル FLASH マイコンを構築することができるようになります.

## Qsys で Nios II システムの ハードウェアを設計

## ●何はともあれ Quartus Prime の新規プロジェ クトを作成

本章では、何もないゼロの状態から Nios II システムの構築をしていきます。まずは図1に従ってQuartus Prime の新規プロジェクトを作成してください。ここではディレクトリ PROJ\_NIOSII\_LED の下にプロジェクト FPGA を生成します。

# ■Qsys を立ち上げて、基本クロック周波数を設定

FPGA 内の中心となる Nios II システムから設計していきましょう. FPGA の最上位階層の下に、ここで設計する Nios II システムがインスタンス化されることになります.

Quartus Prime のメニューから、いきなり**図2**に示す手順で Qsys を立ち上げて作業してください. 今回

の Nios II システム階層のモジュール名は QSYS\_CORE とするので、 Qsys 設計情報は QSYS\_CORE . qsys としてセーブします.

クロック信号とリセット信号を上位階層から受けて Nios II システム内に供給する Clock Source モジュール (インスタンス名: $clk_0$ )がデフォルトで存在して います.ここでは Nios II システム内の基本クロック 周波数を 50MHz に設定しておきます.

## ● Nios II の CPU コアを追加

図3の手順でNios II の CPU コア Nios II Processor を追加してください. ここでは無償のNios II/e を選択します. インスタンス名は自動的に nios2\_gen2\_0 になります. ここでは、インスタンス名は自動的にアサインされたものを変更せずそのまま使います. CPU コアのコンフィグレーションはメモリを追加したあとで設定するので、クロック信号とリセット信号を接続するだけで次に進みます.

#### ● FLASH メモリを追加

**図4**の手順でFLASHメモリを追加してください. インスタンス名は自動的に onchip\_flash\_0 になります.

FLASHメモリは、FPGAのコンフィグレーション情報記憶用のCFMと、ユーザ・メモリ用のUFMから構成されていますが、コンフィグレーション情報の形式によってそれぞれの容量配分が変わります.

ここでは、コンフィグレーション情報の形式を「Single Compressed Image with Memory Initialization」にしておきます。MAX 10 デバイス内に記憶できるコンフィグレーション情報は1種類とし、データは圧縮して、内蔵 RAM の初期化情報も含

見本

# 第 13 市 Nios IIシステムで割り込みを使う方法を マスタしよう

# Nios IIシステムで割り込み

| 本書付属 DVD-ROM 収録関連データ              |                                |                              |  |

|-----------------------------------|--------------------------------|------------------------------|--|

| 格納フォルダ                            | 内 容                            | 備考                           |  |

|                                   |                                | 本章では、このプロジェクトを読者が前章の         |  |

|                                   | Nios IIの割り込みによるフル・カラー          | PROJ_NIOSII_LEDをベースにして作成していく |  |

| CQ-MAX10\Projects\PROJ_NIOSII_INT | LED点滅動作のプロジェクト一式               | 方法を説明する.参考用として提供する.本章で       |  |

|                                   | (Quartus Prime用, Nios II EDS用) | 説明する手順が全て終わった状態のプロジェクト       |  |

|                                   |                                | を格納してある.                     |  |

## ●はじめに

本章では Nios II システムにおける割り込みの使い 方をマスタしましょう。組み込みマイコンで割り込み は頻繁に使うものですが、いざ使おうとしたときに、 C言語での記述方法などでちょっと迷うことがありま す。そのあたりの不安は早い段階で払拭しておきま しょう。

ここでは、Nios II システム内に、周期的に割り込み要求を発生するインターバル・タイマを新規に追加して、その割り込みハンドラ内で LED の色を変えていくプログラムを作成してみます。

## Nios II システムに インターバル・タイマを追加

# ●前章で作成したプロジェクトを複製して新規プロジェクトを作成

前章で作成したプロジェクトをリユースしましょう. 前章の最後の状態, すなわち, FLASH メモリへのコンフィグレーション・データとプログラムの固定

化ができた状態のプロジェクトをベースにしてください

図1に示すように、プロジェクトが含まれるディレクトリPROJ\_NIOSII\_LEDを丸ごと複製して新規ディレクトリPROJ\_NIOSII\_INTを作成してください。

## ■ Quartus Prime でプロジェクトを開く

Quartus Prime で複製したプロジェクト PROJ\_NIOSII\_INT\footnote{The Property of Property

## ■ Qsys で Nios II システム内にインターバル・ タイマを追加

複製したプロジェクト内の Nios II システム QSYS\_CORE.qsys にはインターバル・タイマが 2 個入っていますが、これらはシステム・クロックとタイムスタンプ用に使っています。ここでは、ユーザ割り込み発生用のインターバル・タイマをもう一つ追加します。

図2に示すように作業してください. ここで追加

(1)フォルダ「PROJ\_NIOSII\_LED」を複製して、 フォルダ名を「PROJ\_NIOSII\_INT」に変更する

(2)Quartus Primeを起動して、プロジェクト・ファイル 「PROJ\_NIOSII\_INT¥FPGA¥FPGA.qpf」を開く

PROJ NIOSII LED PROJ NIOSII INT

図1 Quartus Prime のプロジェクトをディレクトリPROJ\_NIOSII\_INT以下に作成 前章で作成したプロジェクトが含まれたディレクトリPROJ\_NIOSII\_LEDをコピーして、ディレクトリ名をPROJ\_NIOSII\_ INTに変更する.

見本

## 第 **14** 章 MAX 10内蔵のA-D変換器を 第 **14** 章 Nios IIシステムで使う方法をマスタしよう

# Nios IIシステムでA-D変換器

| 本書付属 DVD-ROM 収録関連データ                |                            |                               |  |

|-------------------------------------|----------------------------|-------------------------------|--|

| 格納フォルダ                              | 内 容                        | 備考                            |  |

| CQ-MAX10\perojects\peroj_NIOSII_ADC |                            | 本章では、このプロジェクトを読者が前章の          |  |

|                                     | み,アナログ信号のレベルに応じてフ          | PROJ_NIOSII_INT をベースにして作成していく |  |

|                                     | ル・カラー LED の色を変えるプロジ        | 方法を説明する.参考用として提供する.本章で        |  |

|                                     | ェクトー式(Quartus Prime用, Nios | 説明する手順が全て終わった状態のプロジェクト        |  |

|                                     | II EDS用)                   | を格納してある.                      |  |

## ●はじめに

本章では MAX 10 の特長である 12 ビット A-D 変換器の使い方をマスタしましょう. アルテラ社からは, MAX 10 の A-D 変換ハードウェア・ブロックを Nios II システムの中に組み込むためのインターフェース用 IP が提供されており, 簡単に使いこなすことができます.

ここでは、Nios II システム内に A-D 変換器を組み込み、外部のアナログ電圧値に応じてフル・カラー LED の色を変化させる実験をやってみます.

## MAX 10 の A-D 変換器の概要

#### ●アルテラ・モジュラ ADC コアの基本構成

MAX 10 の A-D 変換ハードウェア・ブロックを Nios II システムの中に組み込むためのインターフェース用 IP が、アルテラ・モジュラ ADC コア (Altera Modular ADC Core)です.

この中は大きく分けて二つのブロックから構成されています.

一つは、シーケンサ・コアで、複数のアナログ入力 チャネルの変換シーケンスを制御するためのブロック です、アナログ入力本数とその変換シーケンスは、 Qsys上でアルテラ・モジュラ ADC コアを追加する ときに設定し、ハードウェアとして固定化します。

もう一つはストレージ・コアで、変換結果を保持するストレージを持ち、変換終了割り込みを出力できます。

シーケンサ・コアとストレージ・コアはそれぞれ独立した Avalon-MM インターフェースを持ち、それぞ

れをNios II CPUコアにバス接続する必要があります.

## ● A-D 変換器の入力チャネル

MAX10-FB 基板に搭載した 10M08 (EQFP-144 ピン版) は、12 ビット A-D 変換器を一つ持ち、外部からのアナログ入力チャネルとしては  $CH0 \sim CH8$  の 9 本あります。CH0 は専用端子(ANAIN1) で、 $CH1 \sim CH8$  がディジタル機能との兼用端子(ADC1IN1) へ ADC1IN8) に対応します。 兼用端子 8 本の機能は A-D 変換器を有効化すると全てアナログ入力専用になり、ディジタル機能をアサインすることができなくなるので注意してください。

さらに、MAX 10 は温度計測用ダイオードを内蔵しており、その値を A-D 変換器に取り込むための内部専用チャネル TSD(Temperature Sensing Diode)があります。

## ●複数入力チャネルの変換シーケンス

複数の入力チャネルは、任意にチャネルを切り替えながら最大 64 回連続変換できます。1 回の変換をスロット(Slot)と呼び、各スロットごとに任意の入力チャネルを対応できます。よって、同じ入力チャネルを連続して変換することもできます。

スロットの個数および、各スロットと入力チャネルの対応については、Qsys上でアルテラ・モジュラADCコアを追加するときに設定する必要があります。この設定はハードウェアとして固定化され、ソフトウェアからの変更はできません。

ただし、シングル・サイクル変換モードと連続変換 モードは、ソフトウェアからのレジスタ設定で選択で きます。シングル・サイクル変換モードでは、有効化 1

12

13

14

# 第 **15**章 MAX 10にSDRAMを接続して 第 **15**章 広大なメモリ空間を手に入れよう

# Nios IIシステムでSDRAMアクセス

| 本書付属 DVD-ROM 収録関連データ |                                             |                                                                                                      |  |

|----------------------|---------------------------------------------|------------------------------------------------------------------------------------------------------|--|

| 格納フォルダ               | 内 容                                         | 備考                                                                                                   |  |

|                      | TOOS II システムにSDRAMを接続し<br> T メモリ・チェックを行うプロジ | 本章では、このプロジェクトを読者が前章のPROJ_NIOSII_ADCをベースにして作成していく方法を説明する.参考用として提供する.本章で説明する手順が全て終わった状態のプロジェクトを格納してある. |  |

## ●はじめに

本章では Nios II システムから外部の SDRAM (Synchronous Dynamic RAM)をアクセスする方法をマスタしましょう. MAX10-FB 基板に載せた SDRAM のライト&リード・テストをしてみます. ユーザが自分で MAX10-FB 基板に SDRAM をはんだ付けして実装した時のメモリ・チェックは本章のプロジェクトを使ってください.

FPGAに SDRAM を接続すると広大なメモリ空間を手に入れることができます。 MAX 10 の場合は、プログラムを FLASH メモリに格納して、大規模データを SDRAM に置くことにより、データ処理や画像処理を伴うさまざまな組み込み応用機器に活用できるでしょう。

## SDR 型 SDRAM の概要

## ●レガシーな SDR 型 SDRAM は今でも現役バ リバリ

最近の SDRAM は、DDR (Double Data Rate)型が主流で、DDR2、DDR3、DDR4 などが PC のメイン基板はもちろん、Raspberry Pi などの小型 Linux 基板にも活用されています。 クロックの立ち上がりと立ち下がりの両エッジでデータを転送する非常に高速なSDRAM です。

一方, 今回の MAX10-FB 基板に搭載できる SDRAM はレガシーな SDR(Single Data Rate)型です. クロックの立ち上がりエッジだけに同期してデータ転送する DRAM です.

SDR 型は DDR 型よりもデータ転送速度は遅いのですが、タイミング設計が楽で、特に MAX 10 の 10M08 など DDR メモリとのインターフェースができない FPGA にも簡単に接続することができます.

今回の付属基板に搭載する SDRAM は、256M ビット品  $(32M \text{ バイト}, 16M \text{ ワード} \times 16 \text{ ビット構成})$  または  $512M \text{ ビット品}(64M \text{ バイト}, 32M \text{ ワード} \times 16 \text{ ビット構成})$  を推奨しています。 MAX 10(10M08) の規模で実現できるアプリケーションから見れば、十分なメモリ容量があるといえるでしょう。

SDR型 SDRAMは、既に大手のDRAMメーカは製造していませんが、そうした大手メーカから権利を入手して製造を継続している中小メーカがあり、価格的にもこなれていて今でも現役で活躍しているメモリなのです。

本章では、以下 SDRAM といえば全て SDR 型を指 します。

## ● SDRAM インターフェース信号

図1にSDRAMのインターフェース信号を示します。全ての信号は、CLKの立ち上がりで受け手側に取り込まれます。

SDRAM 側の信号で CKE から BA1, BA0 までは、コマンド系信号です。コマンド系信号の"H"レベルと "L"レベルの組み合わせパターンにより、リードやライトのアクセス方法の指示やリフレッシュの指示などを行います。

DQ15 ~ DQ0 は入出力データです. UDQM, LDQM はデータ入出力マスク信号です. 以下, 簡単に SDRAM のアクセス・タイミングについて説明します

2

6

7

8

11

12

13

14

CQ出版社

フラッシュ・メモリ内蔵 MAX® 10 FPGA

デュアル・ コンフィグ・ フラッシュ・ メモリ

プロセッサ

DDR3 **EMIF**

www.altera.co.jp/max10